DAMC-FMC2ZUP

MTCA.4 ZYNQ UltraScale+ High-Performance FMC/FMC+ Carrier

FMC/FMC+ carrier in MTCA format with Low-Power Xilinx UltraScale+ MPSoC XCZU11EG-L2FFVC1760E FPGA

- Overview

- Features

- Ordering options

- Documentation

- Software/Firmware

Overview

FPGA Low-Power Xilinx UltraScale+ MPSoC XCZU11EG-L2FFVC1760E

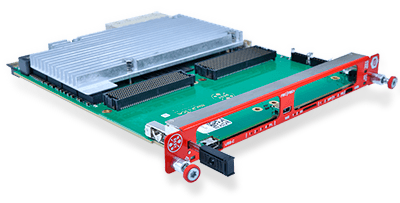

DAMC-FMC2ZUP is a high-end FMC+ carrier in MTCA.4 form factor based on the new ZYNQ UltraScale+ MPSoC. The FPGA mounted on this carrier is the Xilinx ZU11EG. The board has been designed by the MicroTCA TechLab at DESY and it is manufactured by CAEN ELS.

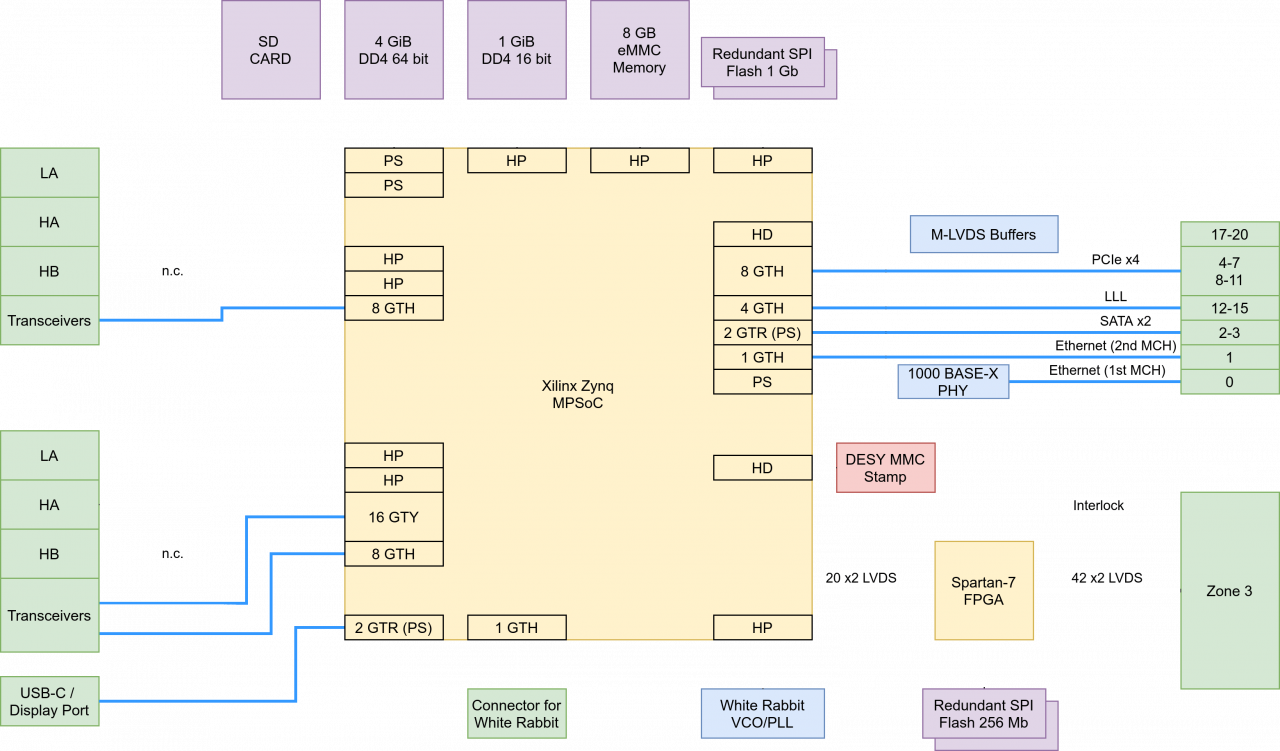

The Programmable Logic (PL) features 653k logic cells, 2920 DSP slices and 48 Multi-Gigabit Transceivers. The Programmable System (PS) is based on a quad-core ARM Cortex-A53 operating at 1.5 GHz.

All MTCA.4 backplane ports are connected to the FPGA. PCI express (port 4-7 and 8-11) is supported in gen. 3.0 x8 configuration. The point-to-point MGT interface (low-latency link) can be used with 4 or 8 lanes width (when PCIe is used in x4 configuration). Gigabit Ethernet (port 0) is connected to Processing System (ARM) and provides convenient access for development and for running application servers.

Eight M-LVDS Timing/Trigger signals and four TCLK lines are also connected. The board features two DDR4 memory interfaces with 64 bit/4GB connected to PS and 16/1GB bits connected to PL, operating at 2400 MT/s and 2666 MT/s respectively.

The board has two FMC sockets: 24 transceivers are routed to the FMC+ socket and can be operated at up to 28.21 Gbps. The other one has a standard HPC connector with 8 transceivers connected, capable of operating at up to 16.375 Gbps. All HA and LA lines are connected on both FMC slots.

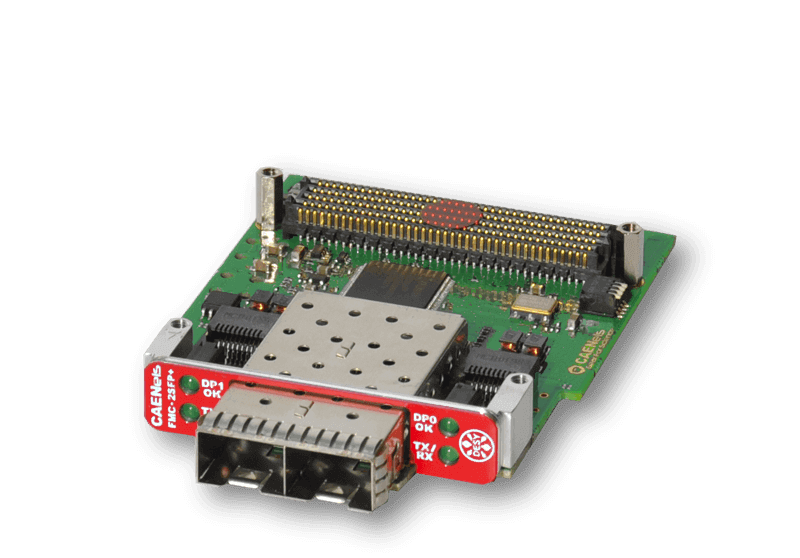

Front panel connector with Gigabit Ethernet interface over SFP+, clock input and two trigger IN/OUT signals.

The board also provides a front panel connector with Gigabit Ethernet interface (over a SFP+), clock input and two trigger in/out signals.

The front panel Gigabit Ethernet connection can be also used as White Rabbit endpoint.

A flexible clocking system with a 16-channel bi-directional cross point switch allows to receive all clocks from and drive all clocks to the backplane (TCLKA, TLCKB, TCLKC, TCLKD) and to and from the FMCs (bi-directional clocks).

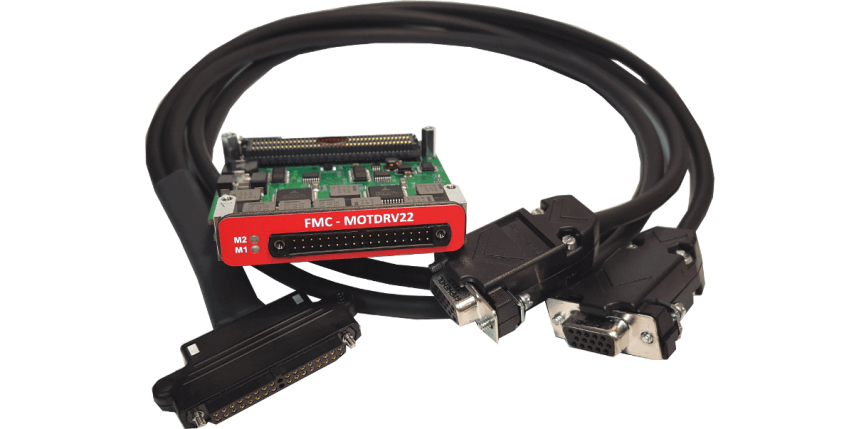

The RTM interface is designed according to class D1.1 and carries full 42 LVDS lines and

2 MGT links. The board can support all existing digital RTMs from DESY, such as DRTM-AD84, DRTM-VM2, DRTM-PZT4.

The ARM Cortex-A53 processor in the MPSoC can run GNU/Linux from a MicroSD

card on the front panel or from an embedded 8GB eMMC. The Processing System is equipped with an USB Type-C interface at the front panel that supports alternate mode. The alternate mode allows to connect to a Display and provides an USB 3.0 interface at the same time, providing the possibility to omit CPU boards in MTCA systems.

Two transceivers from PS are connected to AMC port 2 and 3, allowing attachment of up to two standard off-the-shelf MicroTCA SATA cards with hard drives or SSDs.

The DAMC-FMC2ZUP is supported by all modern development tools as Vivado, HLS, Yocto, Petalinux, SDSoC and SDAccel.

Being supported by all modern development tools by Xilinx, such as Vivado, HLS, Yocto, Petalinux, SDSoC and SDAccel, the DAMC-FMC2ZUP is a board capable of addressing ever-growing needs in terms of processing power, while also reducing development time. Combination of a large FPGA and a powerful CPU provides extreme flexibility required by a general-purpose FMC carrier.

Board Support Package available.

The Board Support Package (BSP) is available on the CAEN ELS GitLab page.

The BSP contains zup meta-layer, Petalinux build guide, Vivado project, and more.

Access to Gitlab is allowed only to the ZUP’s owners.

Features

- FPGA Low-Power Xilinx UltraScale+ MPSoC XCZU11EG-L2FFVC1760E

- One FMC+ Slot with 24 transceivers connected (16 GTY + 8 GTH) - all LA and HA pins are connected

- One standard FMC HPC socket

- USB C-Type connector at the front panel that provides DisplayPort signals and USB 3.0 interface. This allows a standalone system with monitor output and USB host port saving a CPU module

- Zone3 Class D1.1 compliance with full interlock support

- 64-bit 4 GB DDR4 with 2400 MT/s connected to PS - accessible from PL via AXI Bridge

- 16-bit 1 GB DDR4 with 2666 MT/s (2400 MT/s in low-power mode) connected to PL

- Flexible clocking with capability to receive and drive all MTCA backplane clocks (TCLKA, TCLKB, TCLKC, TCLKD, FMC bidirectional clocks) and 3 PLLs to generate clocks for PS, Zone3 and FMC transceivers

- White Rabbit Support (input from front panel, output to backplane via M-LVDS and TCLKs)

- SD-Card slot (connected to PS) accessible via front panel

- 8 GB eMMC Memory connected to PS

- Full MLVDS and interlock receive/drive capability

- JTAG support from on-board connector or AMC backplane (JSM module) with FPGAs, FMCs and RTM as targets

- Full HPM update functionality

Documentation

Last reviewed: 2024-08-29

ⓘ More infoRevision: 2

Last reviewed: 2024-11-05

ⓘ More infoRevision: 1.2

Software/Firmware

Updated: 2023-01-23 - 439.72 kB

ⓘ More info

Version: 2.01